|

通常的教训是避免过去的ISA“优化”。经验和教训在简单性和性能下列出的许多指令集特性可以互换,因为这只是设计的偏好问题,但不管它们出现在哪里,它们都很重要。以上摘自RISC-V中文手册。

既然RISC-V具备这些优势,那我们再来探讨一下RISC-V的现状。时至今日,RISC-V指令集的支持工具已经相对完善。芯片设计公司不再担心工具链问题,只需专注于芯片设计,RISC-V社区已经提供了完整的工具链,并且RISC-V基金会将会持续维护该工具链。 IAR现已推出适用于RISC-V的工具链新版本。1.20版增加了对基本指令集RV32E的支持,以及对原子操作(A)的标准扩展。这使OEM以及SoC供应商能够根据应用程序或产品所需的确切定义来设计自定义内核。通过不断增加更多的支持和功能,IAR Systems可使这些公司充分利用领先的嵌入式开发工具链的功能来开发基于定制内核的应用程序。

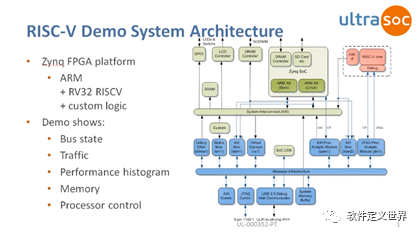

UltraSoC宣布将通过OpenHW集团提供其业界领先的RISC-V跟踪编码器的开源实现。可用的生产级、符合标准的处理器跟踪解决方案是开发进步的关键推动力,其支持基于开源处理器为开发创建开放的、商业级的生态系统。

Microchip及其Mi-V合作伙伴提供了基于RISC-V的SoCFPGA以及其Mi-V生态系统,正在推动嵌入式领域的创新。Mi-VRISC-V生态系统是由Microchip和众多第三方开发的一套全面的工具和设计资源,以全面支持RISC-V设计。

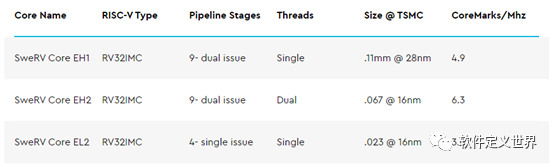

今年2月,西部数据(Western Digital)发布了基于RISC-V指令集的自研通用架构SweRV,这是西部数据努力引领ISA(指令集架构)及其生态系统的一部分,也是他们向免授权CPU核心过渡的一部分。迄今为止西部数据已经开发出了三款RISC-V核心的产品。

12月11日Cobham Gaisler在加利福尼亚州圣何塞举行的RISC-V峰会上宣布,它将发布实现RISC-V指令集体系结构(ISA)的处理器IP内核新线。该系列的第一款产品NOEL-V处理器IP内核将于12月25日上市,可下载到Xilinx的Kintex UltraSCALE FPGA中。

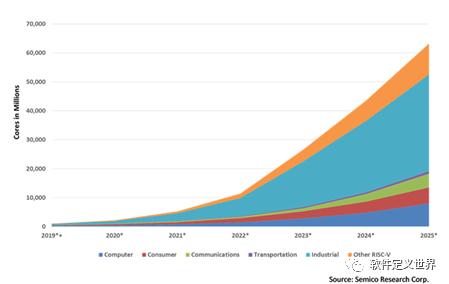

根据分析机构Semico Research的最新报告《RISC-V市场分析:新兴市场》估计,到2025年,市场将总共消费624亿个RISC-VCPU内核,预计工业领域将是最大的细分市场,拥有167亿个内核。Semico预测RISC-V CPU内核的复合年增长率(CAGR),估计包括计算机,消费者,通讯,运输和工业市场在内的细分市场在2018年至2025年之间的平均复合年增长率为146.2%。

RISC-V 基金会于 11 月 25 日正式宣布,总部注册地将从美国迁往中立国家瑞士,只待瑞士监管机构的最终审核。此举在于试图避免受到地缘政治氛围的负面影响

RISC-V在中国的火热程度甚至超过美国,这背后也有地缘政治的原因。伴随着中美之间的贸易摩擦,科技冷战也开始打响。美国政府加大美国先进技术对中国企业的出口管制,迫使以华为为首的中国高科技企业寻求自主创新之道。虽然多年来中国科研院所和企业先后购买Intel、AMD、MIPS和Arm架构授权,但在微处理器研发和产业化方面都没能形成突破性进展,更谈不上“自主可控”了。RISC-V恰逢其时,短短两年时间内就在中国半导体业界形成“芯芯之火”的燎原之势。

专门负责RISC-V架构及指令标准制定的RISC-V基金会特别重视中国市场,不但有专门的中国委员会,还积极推动与中国RISC-V机构合作。立足上海的中国 RISC-V 产业联盟(CRVIC)以围绕RISC-V的芯片设计产业发展为主,而立足北京的中国开放指令生态(RISC-V)联盟CRVA则以RISC-V生态的设计工具和软件开发为主。深圳在今年11月份将RISC-V的开山鼻祖 DavidPatterson教授请来并在清华-伯克利深圳学院(TBSI)成立以Patterson教授命名的RISC-V国际开源实验室(RIOS),RIOS在西班牙语里是“河流”的意思,寓意这个RISC-V研究机构将像河流一样汇聚来自全球的资源和智力,催生和孕育RISC-V生态的健康发展,并推动RISC-V发展成为未来50年的计算架构标准。

2018 年下半年起,除了早早入局的华为和阿里,还有有华米、中天微、乐鑫等代表性企业表示支持 RISC-V。 首先,华米科技发布黄山一号芯片,没有采用传统的 ARM 架构处理器,成为全球第一款采用 RISC-V 开源指令架构的穿戴式处理器,相比 ARM Cortex-M4 处理器的运算效率高出 38%,凸显 RISC-V 与低功耗市场的契合。

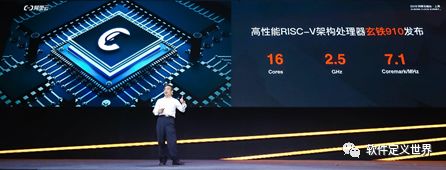

阿里巴巴旗下的中天微和平头哥也双双拿出成果。前者宣布推出支持 RISC-V 第三代指令系统架构处理器 CK902,后者在今年推出了运用 12 纳米工艺,搭载 16 个核心,号称“业界最强”的 RISC-V 处理器玄铁 910。

成立于 2008 年的上海乐鑫公司也基于RISC-V指令集架构开发物联网芯片,致力于研发 WiFi 和蓝牙组成的双模物联网。此外,还有芯来、君正、芯原和核芯等中国公司也在从事 RISC-V 架构的相关研发

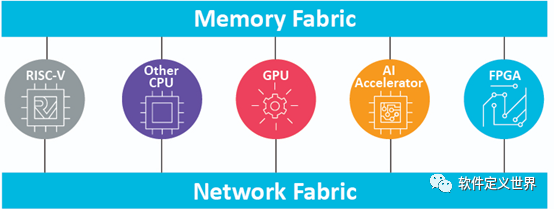

随着RISC-V生态建设的不断推进,我们相信未来一段时间内,RISC-V将与ARM同行发展,即一个设计中,既能使用ARM也能使用RISC-V,或者同一颗芯片里,可以同时有两种内核。期望未来RISC-V的生态环境建设从围绕芯片设计转向开发者教育和实践阶段,为培养更多的行业人才而努力。

参考资料及更多信息可访问以下网站获取: RISC-V基金会:https://riscv.org/ 中国开放生态联盟:http://crva.io/ IAR公司:https://www.iar.com/

|  /2

/2