有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

奇妙的设计思路克服了几个主要的障碍,但它不是通向高性能的途径。

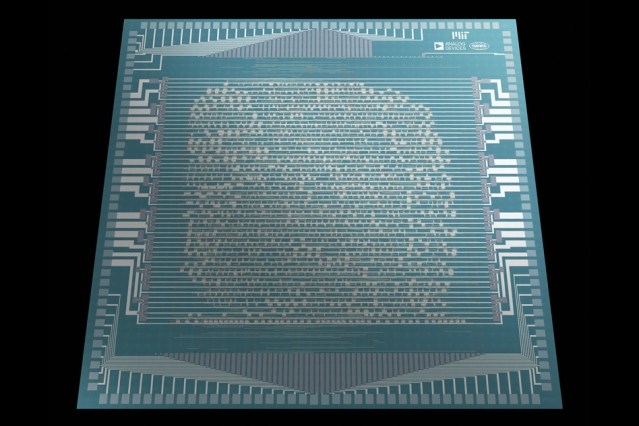

RV16X-NANO(图片来源:MIT)

我们似乎不能像过去那样可以不断缩小硅基处理器的元件,这促使材料科学家们在硅片之外另辟蹊径。首选方法就是碳纳米管,碳纳米管以半导体形式自然存在,拥有出色的电气特性,而且极小。遗憾的是,已证明让纳米管在需要它们的地方生成极其困难,而操纵纳米管、将它们放在合适的位置一样困难。克服这些挑战方面已取得了一些进展,但展示成果的通常是在很有限的演示中。

现在,研究人员已经使用碳纳米管制造了一种符合 RISC-V 标准的通用处理器,它可以处理 32 位指令,并进行 16 位存储器寻址。性能不值得大书特书,但该处理器成功地执行了传统演示程序“Hello world!”的变体。这是一件出色的杰作,但并非所有研究人员的解决方案都有可能带来高性能处理器。

我们能克服这个问题 碳纳米管存在好多问题。首先,虽然纳米管以半导体形式自然存在,但它们是结合该过程和使用金属纳米管生成的。虽然可以净化半导体版本,但纯净度往往在 99.9%左右就趋于平稳。这在许多情况下很好,但是当处理器有数百万个纳米管时,这显然不顶用。纳米管并不自然形成 p 型半导体或 n 型半导体(分别偏向于传输正电荷或负电荷)。在硅中,这些特性是通过添加少量额外元素来决定的,这个过程名为掺杂(doping)。但是纳米管实在太小了,极难掺杂。

其他问题源自需要将纳米管放在极其精确的位置才能让任何电子元件工作。我们还没有弄清楚如何让纳米管在任何特定的位置生长,因此科学家不得不分开来生长纳米管,然后让它们在表面上沉积。遗憾的是,这个过程通常会生成一层薄膜状的方向随机的纳米管,夹杂着大量纳米管堆积形成的聚合体。还会有几个随机放置的金属纳米管潜藏在这层薄膜内。

新处理器由麻省理工学院(MIT)的研究人员和 Analog Devices 公司的科学家携手研制,他们找到了克服所有这些问题的方法。

第一个办法是接受纳米管的混乱。研究人员做了一个拥有金属元件的硅表面,金属元件大得足以保证几个纳米管通常可以填补金属之间的间隙,而不是试图将一个纳米管放在需要它的每个地方。为了去除聚合体,他们在纳米管上沉积了一层材料,然后通过声波降解法再将其打碎。这层材料与聚合体粘在一起,但使纳米管底层不受干扰。

接下来,为了将纳米管限制在需要它的地方,研究人员只需蚀刻掉纳米管的大部分层,让它们处在需要的地方。然后,他们在纳米管的上方添加了可变的氧化物层。氧化物的具体特性结合用于连接的不同金属,就可以根据需要将纳米管转变成 p 型半导体或 n 型半导体。虽然这个过程更类似掺杂恰好含有纳米管的区域,但它可以有效地控制各个接点的行为。

仍潜藏在其中的那些金属纳米管呢?研究人员干脆让它们留在原地,并在芯片设计方面做了变通工作。

合理的逻辑布局 虽然芯片的功能单元执行两个数字相加之类的操作,但这些单元用一堆较小逻辑门做成,这些逻辑门执行简单的功能:NOT 翻转位的值;如果两个输入值均为 1,逻辑 AND 取值为 1,诸如此类。常常有多种方法来构造这些逻辑门以形成相同的功能单元。因此,可以使用 5 个 AND 和 7 个 NOR 组成的正确排列对两个数字相加,也可以使用 6 个 NOT 和 4 个 NAND 来完成。(注意:那些数字是完全编造的。)

研究人员在新芯片背后的主要思路是,相比另一些逻辑功能,某些逻辑功能对金属纳米管不太敏感。因此,他们修改了一个开源 RISC 设计工具充分考虑到这一点。结果是芯片设计根本没有对金属碳纳米管极为敏感的逻辑门。

研究团队将由此获得的芯片称为 RV16X-NANO,该芯片旨在处理 RISC-V 架构的 32 位长指令。存储器寻址限制在 16 位,功能单元包括指令获取、解码、寄存器、执行单元和写回存储器。RV16X-NANO 总共使用了 14000 多个独立晶体管,操纵碳纳米管以制作晶体管带来的成品率高达 100%。换句话说,那 14000 个门个个有效。

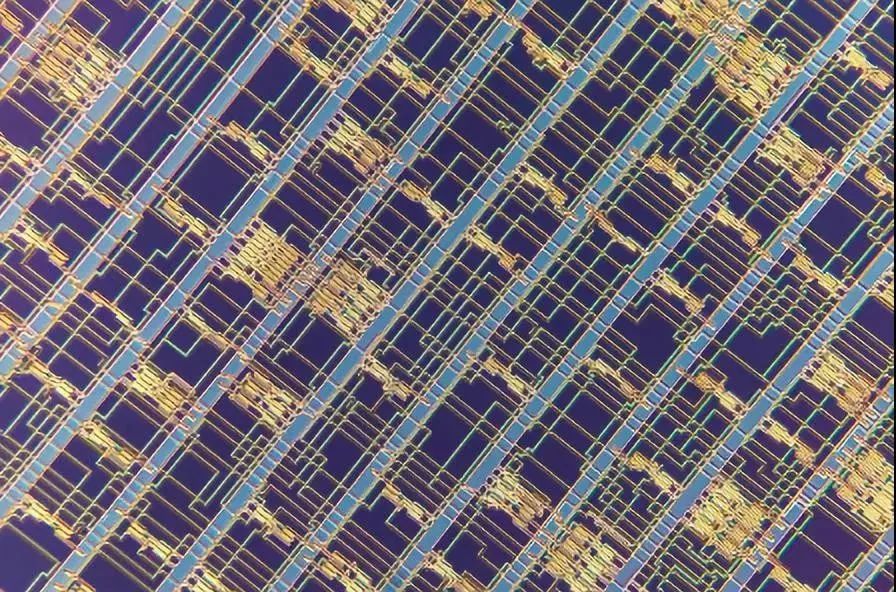

它也被认为是 3D 芯片,原因在于纳米管层下面的金属触点用于在不同晶体管之间路由传输信号,而纳米管上方的另外一层金属触点用于在芯片内供电。

Hello world,碳纳米管版

最关键的是,它很管用。你从上图可以看出,它成功地执行了传统“Hello World”程序的变体,该程序通常用来对不同编程语言的语法作一个简介。

路线图还是兜圈子? 研究人员在论文中主要介绍了可以改善现有设计的种种方法。比如说,沟道长度是纳米管连接的金属触点之间的距离。这个长度有助于设定时钟速度;对于 RV16X-NANO 而言,时钟速度仅为 10kHz。金属触点还必须很宽,才能确保有足够的纳米管来连接它们。我们在理论上知道两者都有望加以改进,提高时钟速度无疑是这方面的一条出路。

但由于这种设计需要容忍金属纳米管(而不是去除金属纳米管),因此每个晶体管总是需要有多个纳米管。这种设计还需要足够宽,以便有几个方向不对的纳米管仍会留下足够的空间,以便其他纳米管形成功能触点。而这意味着元件必然会比我们想要的更大,需要更长的时间在状态之间切换。

通过架构克服金属纳米管的存在需要的晶体管总数增加,这可能也带来了成本,不过这可能因某个特定功能单元的用途而有所变化。

这些问题被解决的前景不一样。这个过程没有哪个方面在阻止门长度缩小,门长度缩小可促使时钟速度增加;这正是研究人员可以立即尝试的。如果我们可以想出一种制造纯半导体纳米管的方法,另外一些问题就会迎刃而解。这显然是人们在努力的方向,但在这个问题得到解决之前,这种设计的用途仍然有限。

但这里的最终目标是制造出单纳米管晶体管,这需要能够控制它们在芯片上的位置。而这项工作并没有让我们更接近这个目标。

总的来说,这是一项出色的工程杰作,也是一次重要的验证:证明我们可以将碳纳米管与现有的芯片制造工艺集成起来,并且与处理器运行所必需的其他电子元件集成起来。但在解决阻碍碳纳米管充分发挥其潜力的问题方面,它并没有取得太大的进展。

|  /2

/2