有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

本帖最后由 小飞飞 于 2021-2-21 14:30 编辑

大道至简——RISC-V架构之魂(上)

大道至简——RISC-V架构之魂(中)

大道至简——RISC-V架构之魂(下)

“大道至简——RISC-V架构之魂”——分成上中下三篇,本文是上篇。

2.12 特权模式. RISC-V架构定义了三种工作模式,又称特权模式(Privileged Mode):

RISC-V架构定义M Mode为必选模式,另外两种为可选模式。通过不同的模式组合可以实现不同的系统。

RISC-V架构也支持几种不同的存储器地址管理机制,包括对于物理地址和虚拟地址的管理机制,使得RISC-V架构能够支持从简单的嵌入式系统(直接操作物理地址)到复杂的操作系统(直接操作虚拟地址)的各种系统。

2.13 CSR寄存器

. RISC-V架构定义了一些控制和状态寄存器(Control and Status Register,CSR),用于配置或记录一些运行的状态。CSR寄存器是处理器核内部的寄存器,使用其自己的地址编码空间和存储器寻址的地址区间完全无关系。

CSR寄存器的访问采用专用的CSR指令,包括CSRRW、CSRRS、CSRRC、CSRRWI、CSRRSI以及CSRRCI指令。

2.14 中断和异常. 中断和异常机制往往是处理器指令集架构中最为复杂而关键的部分。RISC-V架构定义了一套相对简单基本的中断和异常机制,但是也允许用户对其进行定制和扩展。

2.15 矢量指令子集

. RISC-V架构目前虽然还没有定型矢量(Vector)指令子集,但是从目前的草案中已经可以看出,RISC-V矢量指令子集的设计理念非常的先进,由于后发优势及借助矢量架构多年发展成熟的结论,RISC-V架构将使用可变长度的矢量,而不是矢量定长的SIMD指令集(譬如ARM的NEON和Intel的MMX),从而能够灵活的支持不同的实现。追求低功耗小面积的CPU可以选择使用长度较短的硬件矢量进行实现,而高性能的CPU则可以选择较长的硬件矢量进行实现,并且同样的软件代码能够彼此兼容。

2.16 自定制指令扩展

. 除了上述阐述的模块化指令子集的可扩展、可选择,RISC-V架构还有一个非常重要的特性,那就是支持第三方的扩展。用户可以扩展自己的指令子集,RISC-V预留了大量的指令编码空间用于用户的自定义扩展,同时,还定义了四条Custom指令可供用户直接使用,每条Custom指令都有几个比特位的子编码空间预留,因此,用户可以直接使用四条Custom指令扩展出几十条自定义的指令。

请参见《实例讲解进驻Google两位大神主推的异构计算与RISC-V》了解更多协处理器扩展的信息。

2.17 总结与比较

. 处理器设计技术经过几十年的衍进,随着大规模集成电路设计技术的发展直至今天,呈现出如下特点:

如上种种这些因素,使得很多早期的RISC架构设计理念(依据当时技术背景而诞生),时至今日不仅不能帮助现代处理器设计,反而成了负担桎梏。某些早期RISC架构定义的特性,一方面使得高性能处理器的硬件设计束手束脚;另一方面又使得极低功耗的处理器硬件设计背负不必要的复杂度。

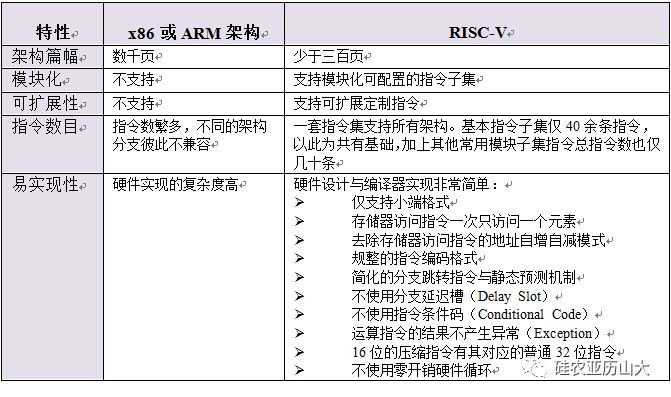

得益于后发优势,全新的RISC-V架构能够规避所有这些已知的负担,同时,利用其先进的设计哲学,设计出一套“现代”的指令集。本节再次将其特点总结如表2所示。

表2 RISC-V指令集架构特点总结

一言以蔽之,RISC-V的特点在于极简、模块化以及可定制扩展,通过这些指令集的组合或者扩展,你几乎可以构建适用于任何一个领域的微处理器,比如云计算、存储、并行计算、虚拟化/容器、MCU、应用处理器和DSP处理器等。

3 RISC-V和其他开放架构有何不同

. 如果仅从“免费”或“开放”这两点来评判,RISC-V架构并不是第一个做到免费或开放的处理器架构。

下文将通过论述几个具有代表性的开放架构,来分析RISC-V架构的不同之处以及为什么其他开放架构没能取得足够的成功。

3.1 平民英雄——OpenRISC

. OpenRISC是OpenCores组织提供的基于GPL协议的开放源代码RISC处理器。

OpenRISC具有以下特点:

OpenRISC被应用到很多公司的项目之中。可以说,OpenRISC是应用非常广泛的一种开源处理器实现。

OpenRISC的不足之处在于其侧重于实现一种开源的CPU Core,而非立足于定义一种开放的指令集架构,因此其架构的发展不够完整,指令集的定义也不具备上节中提到的RISC-V架构的优点,更加没有上升到成立专门的基金会组织的高度。OpenRISC更多的时候被认为是一个开源的Core,而非一种优美的指令集架构。此外,OpenRISC的许可证为GPL,这意味着所有的指令集改动都必须开源(而RISC-V则无此约束)。

3.2 豪门显贵——SPARC. SPARC架构作为经典的RISC微处理器架构之一,SPARC最早于1985年由Sun电脑所设计。SPARC也是SPARC国际公司的注册商标之一,这家公司于1989年成立,目的是向外界推广SPARC架构以及为该架构进行兼容性测试。该公司为了推广SPARC的生态系统,SPARC国际公司将标准开放,并授权予多家生产商采用,包括德州仪器、Cypress半导体和富士通等。由于SPARC架构也对外完全开放,因此,也出现了完全开放源码的LEON处理器。不仅如此,Sun公司还于1994年推动SPARC v8架构成为IEEE标准(IEEE Standard 1754-1994)。

由于SPARC架构的初衷是面向服务器领域而设计,其最大的特点是拥有一个大型的寄存器窗口,符合SPARC架构的处理器需要实现从72到640个之多的通用寄存器,每个寄存器宽度为64bits,组成一系列的寄存器组,称之为寄存器窗口。

这种寄存器窗口的架构,由于可以切换不同的寄存器组快速地响应函数调用与返回,因此,能够产生非常高的性能,但是这种架构由于功耗面积代价太大,而并不适用于PC与嵌入式领域处理器。而SPARC架构也不具备模块化的特点,使得用户无法裁剪和选择。很难作为一种通用的处理器架构对商用的x86和ARM架构形成替代。

设计这种超大服务器CPU芯片又非普通公司与个人所能涉足,而有能力设计这种大型CPU的公司也没有必要投入巨大的成本来挑战x86的统治地位。随着Sun公司的衰弱,SPARC架构现在基本上退出了人们的视野。感兴趣的读者请在网络上自行搜索文章《再见SPARC处理器,再见Sun》

3.3 名校优生——RISC-V

. 关于RISC-V在伯克利大学诞生的经历,本节在此不做重复赘述。

因为多年来在CPU领域已经出现过多个免费或开放的架构,很多高校也在科研项目中推出过多种指令集架构。因此,当笔者第一次听说RISC-V之时,以为又是一个玩具,或纯粹学术性质的科研项目而不以为意。

直到笔者亲自通读了一遍RISC-V的架构文档,不禁为其先进的设计理念所折服。同时,RISC-V架构的各种优点也得到了众多专业人士的青睐好评和众多商业公司的相继加盟。并且2016年RISC-V基金会的正式启动在业界引起了不小的影响。如此种种,使得RISC-V成为至今为止最具备革命性意义的开放处理器架构。

“大道至简——RISC-V架构之魂”——分成上中下三篇,本文是下篇。

(全文完) |

/2

/2