有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

本帖最后由 ニコ·ロビン 于 2020-8-8 23:05 编辑

本文目录

RISC-V指令集架构介绍 通用寄存器模型 RISC-V特权级 RISC-V指令集描述 RISC-V总结

RISC-V指令集架构介绍

RISC-V(英文发音为"risk-five")是一个全新的指令集架构,该架构最初由美国加州大学伯克利分校的EECS部门的计算机科学部门的Krste Asanovic教授、Andrew Waterman和Yunsup Lee等开发人员于2010年发明。

其中"RISC"表示精简指令集,而其中"V"表示伯克利分校从RISC I开始设计的第五代指令集。

2010年,加州大学伯克利分校的研究团队分析了ARM、MIPS、SPARC、X86等多种指令集,发现这些指令集不仅复杂度不断提升,且还存在知识产权风险,而处理器架构种类和处理能力并无直接关联。

针对以上问题,该小组设计并推出了一套基于BSD协议许可的免费开放的指令集架构RISC-V,其原型芯片也于2013年1月成功流片。

RISC-V指令集具有性能优越,彻底免费开放两大特征。

RSIC-V的设计目标是能够满足从微控制器到超级计算机等各种复杂程度的处理器需求,支持从FPGA、ASIC乃至未来器件等多种实现方式,同时能够高效地实现各种微结构,支持大量定制与加速功能,并与现有软件及编程语言可良好适配。

RISC-V产业生态正进入快速发展期。加州大学伯克利分校在2015年成立非盈利组织RISC-V基金会,该基金会旨在聚合全球创新力量共同构建开放、合作的软硬件社区,打造RISC-V生态系统。

三年多来,谷歌、高通、IBM、英伟达、NXP、西部数据、Microsemi、中科院计算所、麻省理工学院、华盛顿大学、英国宇航系统公司等100多个企业和研究机构先后加入了RISC-V基金会。

RISC-V基金会负责维护RSIC-V指令集标准手册与架构文档,每年RISC-V基金会都会举办各种专题讨论会和全球活动,将广阔的生态系统聚集在一起,讨论当前和未来RISC-V项目和实施,以促进RISC-V阵营的交流和发展。

一款指令集架构能否取得成功,很大程度依赖于软件生态环境。当前可用的RISC-V软件工具包括GNU编译器集合(GCC工具链、GDB调试器),LLVM工具链,OVPsim仿真器(以及RISC-V快速处理器模型库),Spike仿真器和QEMU模拟器。

当前支持该指令集架构的操作系统包括FreeRTOS、SylixOS、RT-Thread、Linux等。

RTRISC-V架构在短时间内还无法撼动x86和ARM架构,但是随着越来越多的公司和项目采用RSIC-V架构的处理器,相信RSIC-V的软件生态会逐渐壮大起来。

通用寄存器模型

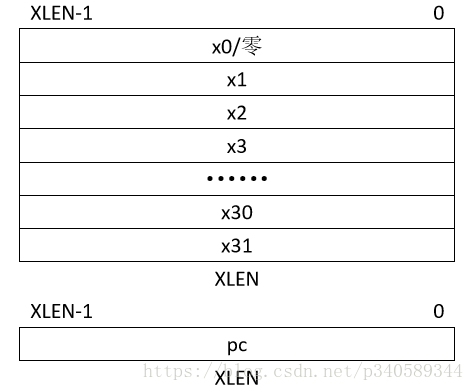

RISC-V具有32个整数寄存器x0~x31,其中31个通用寄存器x1~x31,它们保存了整数数值,寄存器x0是硬件连线的常数0。

当实现浮点扩展时具体32个浮点寄存器f0~f31。对于RV32,其x寄存器是32位宽度的,对于RV64,它们是64位宽度的。

其中RISC-V寄存器调用约定如下图:

RISC-V调用约定尽可能在寄存器中传递参数,其多达8个整数寄存器a0-a7,和多达8个个浮点寄存器fa0-fa7用于这个目的。

函数的返回值存放在整数寄存器a0和a1、浮点寄存器fa0和fa1中。返回值包含1个或者2个浮点值的结构体时候通过浮点寄存器返回,其他返回值能放入a0和a1。

更大的返回值都全部通过存储器返回,调用者分配这些存储器区域,并将它作为第一个隐藏参数传递给被调用者。

在标准RISC-V调用约定中,栈是向下增长并且栈指针总是对齐到16字节。

除了参数寄存器和返回值寄存器之外,7个整数寄存器t0-t6和12个浮点寄存器ft0-ft11是临时寄存器,它们在调用过程中被破坏,如果后面还有使用的话,在调用者中必须先保存。

12个整数寄存器s0-s11和12个浮点寄存器fs0-fs11在调用过程后被保持不变,如果需要使用的 话,在被调用者中必须保存。

RISC-V特权级

RISC-V定义了四种特权级模式。不同的特权级包含多个 CSR(control and status register,控制和状态寄存器)寄存器。

四种特权级信息如下表1.1:

特权级被用于在不同的软件栈部件之间提供保护,试图执行当前特权模式不允许的操作,将导致一个异常的产生。

机器级是最高级特权,也是RISC-V硬件平台唯一必须的特权级。

运行于机器模式(M-mode)下的代码是固有可信的,因为它可以在低层次访问机器的实现。

用户模式(U-mode)和管理员模式(S-mode)被分别用于传统应用程序和操作系统,而 Hypervisor 模式(H-mode)则是为了支持虚拟机监视器。

所有硬件实现必须提供 M-mode,因为这是唯一的模式可以不受限制地访问整个机器。

最简单的 RISC-V 实现可以仅提供M-mode,虽然这样做不能为防止不正确的、恶意应用代码提供保护。

许多RISC-V实现还支持至少一个用户模(U-mode)以对系统的其他部分进行 保护,防止被应用程序代码破坏。

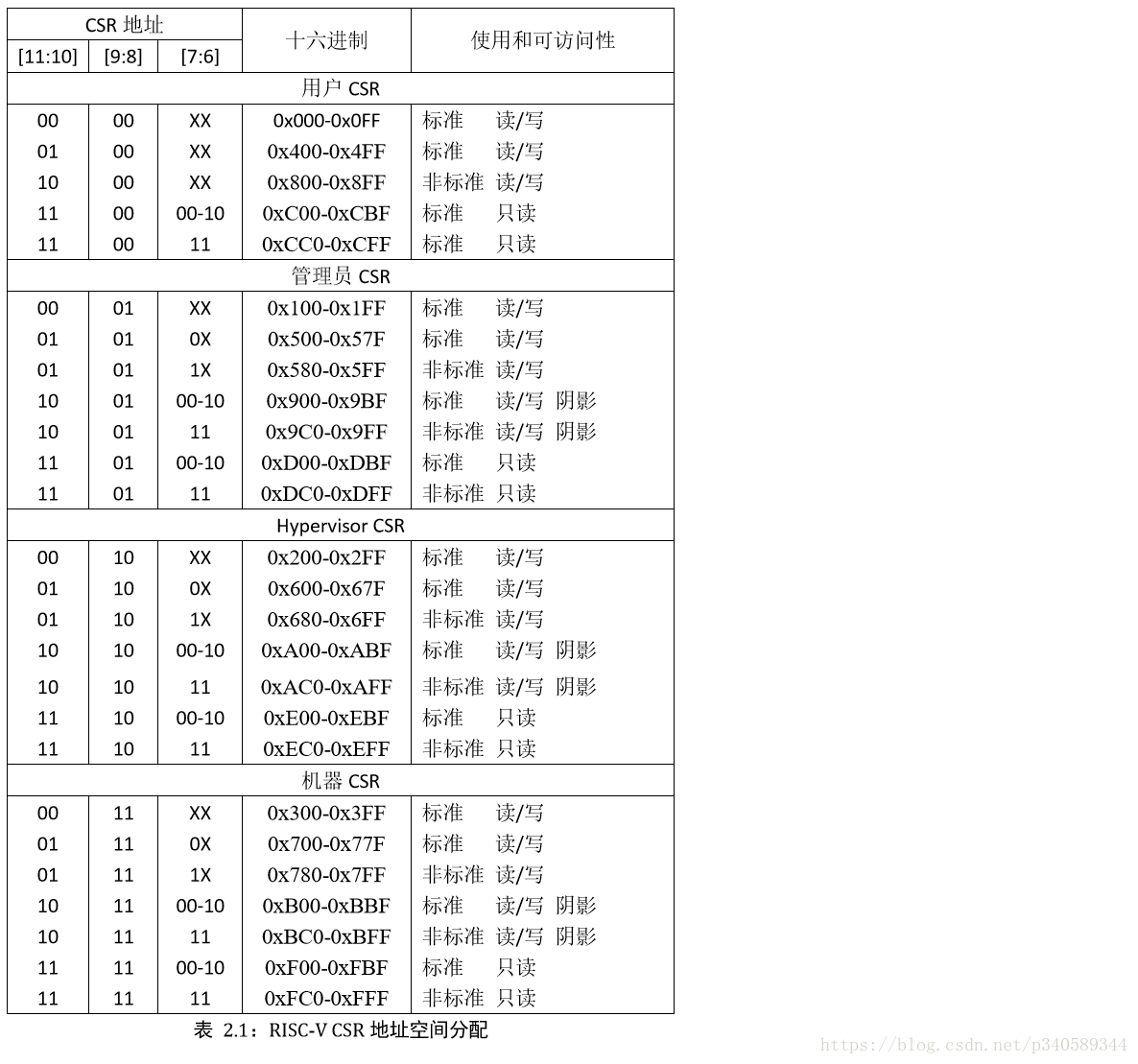

标准 RISC-V ISA 设置了一个 12 位的编码空间(csr[11:0])可用于 4096 个 CSR。

根据约定,CSR 地址的高 4 位(csr[11:8])用于编码CSR根据特权级读写的可访问性。

最高2位(csr[11:10])指示这个寄存器是否是可以读/写(00、01或者10),还是只读 的(11)。后面 2 位(csr[9:8])指示了能够访问这个 CSR 所需要的最低特权级(用户级是 00, 管理员级是 01)。

试图访问一个不存在的CSR将产生一个非法指令异常。

试图访问一个没有相应特权的CSR或者写一个只读寄存器,也将产生一个非法指令异常。

一次读/写寄存器可能包含了某 些位是只读的,此种情况下,写入只读位被忽略。

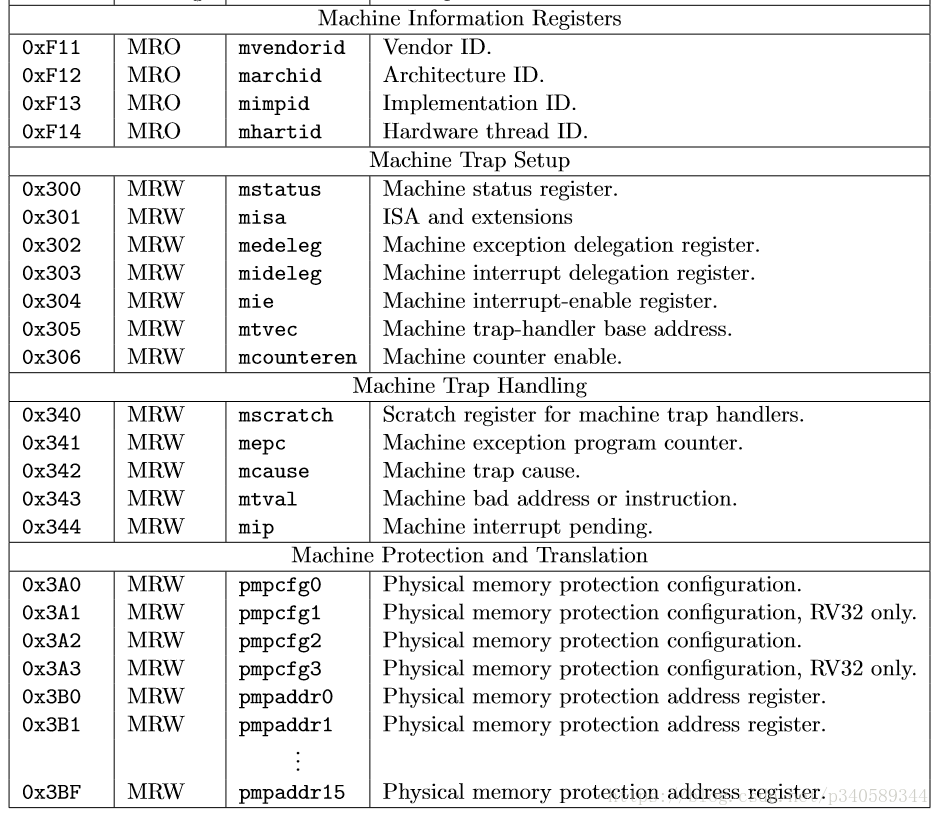

CSR相关寄存器相关描述可参考特权级指令手册,其中机器模式寄存器如下图:

用于读取CSR的汇编语言伪指令CSRR rd, csr被编码为CSRRS rd, csr, x0。

用于写CSR的汇编语言伪指令CSRW csr, rs1 被编码为 CSRRW x0, csr, rs1,而伪指令 CSRWI csr, zimm 被编码 为 CSRRWI x0, csr, zimm。 |  /2

/2