有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

本帖最后由 皋陶 于 2020-8-26 17:49 编辑

The Processor Abstract:

This chapter describes how processors exploit implicit parallelism. 它包含对实现处理器所使用的原理和技术的解释,首先是高度抽象和简化的概述。概述后的一节建立一个数据路径,并构造一个简单版本的处理器,足以实现一个指令集,如RISC-V。本章的大部分内容涵盖了一个更实际的流水线RISC-V实现,最后一节开发了实现更复杂指令集(如x86)所需的概念。

4.1

Introduction

Chapter1 explains the performance of a computer is determined by three key factors——instruction count*(IC) ,clock cycle time,

and clock cycles per instruction (CPI),

the compiler and the instruction set architecture determine IC required for a given program.

implementation of the processor determines both the clock cycle time and the number of clock cycles per instruction(CPI)

在本章中,我们为两种不同的RISC-V指令集实现构造了数据路径和控制

本节、第4.5节:介绍了流水线的基本概念

4.10:Current trends are covered

4.11: describes the recent Intel Core i7 and ARM CortexA53 architectures.

4.12 shows how to use instruction-level parallelism to more than double the performance of the matrix multiply from Section 3.9. These sections provide enough background to understand the pipeline concepts at a high level.

4.3、4.4、4.6:可更深入地了解处理器及其性能

4.2、4.7、4.9:学习如何构建处理器

For readers with an interest in modern hardware design, 4.13 describes how hardware design languages and CAD tools are used to implement hardware, and then how to use a hardware design language to describe a pipelined implementation. It also gives several more illustrations of how pipelining hardware executes

A Basic RISC-V Implementation

我们将研究一个包含核心RISC-V指令集子集的实现:加载双字(ld),存储双字(sd),算术逻辑指令add、sub和或条件分支指令分支(beq)。 此子集不包括所有整数指令(对于例如,shift、multiply和divide),也不存在任何浮点指令。但是,它说明了创建数据路径和设计控件时使用的关键原则。其余指令的实现类似。

我们将有机会了解指令集体系结构如何决定implementation,以及各种实现策略的选择如何影响计算机的时钟速率和CPI。

An Overview of the Implementation

在第二章中,我们研究了核心RISC-V指令,包括整数算术逻辑指令、内存引用指令和分支指令。要实现这些指令,需要做的很多事情是相同的,与指令的确切类别无关。对于每一条指令,前两步是相同的

1. Send the program counter (PC) to the memory that contains the code and fetch the instruction from that memory.

2、读取一个或两个寄存器(使用指令字段选择要读取的寄存器,对于ld指令,我们只需要读取一个寄存器,但大多数其他指令需要读取两个寄存器。) 在这两个步骤之后,完成指令所需的操作取决于指令类。幸运的是,对于三个指令类(内存引用、算术逻辑和分支,memory-reference, arithmetic-logical, and branches)中的每一个,这些操作基本上是相同的,与确切的指令无关。

RISC-V指令集的简单性和规律性通过使许多指令类的执行相似而简化了实现.例如,所有指令类在读取寄存器后使用算术逻辑单元(ALU)。内存引用指令使用ALU进行地址计算.用于操作执行的算术指令,以及用于相等测试的条件分支

使用ALU后,完成各种指令类所需的操作不同:内存引用指令需要访问内存以读取加载数据或写入存储数据;算术逻辑或加载指令必须将数据从ALU或内存写回寄存器;最后,对于条件分支指令,我们可能需要根据比较来更改下一条指令的地址;否则,PC机应该增加4以获得下一条指令的地址。

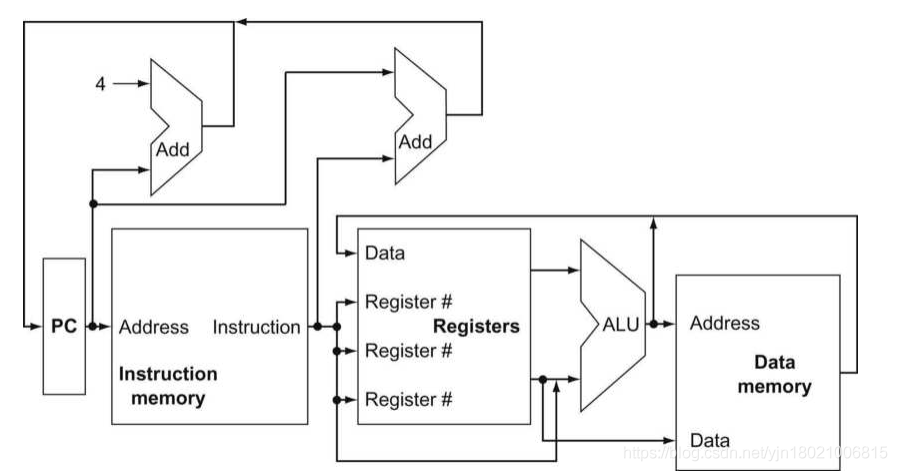

图4.1:

所有指令从使用程序计数器向指令存储器提供指令地址开始

获取指令后,指令使用的寄存器操作数由该指令的字段指定。一旦获取了寄存器操作数,就可以操作它们来计算内存地址(用于加载或存储)、计算算术结果(用于整数算术逻辑指令)或相等检查(用于分支)。

如果指令是算术逻辑指令,则ALU的结果必须写入寄存器。如果操作是加载或存储,the ALU result is used as an address to either store a value from the registers or load a value from memory into the registers.

分支需要使用ALU输出来确定下一个指令地址,该地址要么来自加法器(PC和分支偏移相加),要么来自将当前PC增加4的加法器。

箭头用于引导读者了解信息是如何流动的。连接各功能单元的粗线表示由多个信号组成的总线。点表示多个信号线交叉了

图4.1显示了RISC-V的实现,着重于各个功能单元及其互连。尽管此图显示了通过处理器的大部分数据流,但它忽略了指令执行的两个重要方面。

首先,在几个地方,图4.1显示了从两个不同的来源发送到特定单元的数据。例如,写入PC的值可以来自两个加法器中的一个,写入寄存器文件的数据可以来自ALU或数据存储器,而到ALU的第二个输入可以来自寄存器或指令的立即字段。

实际上,这些数据线不能简单地连接在一起;我们必须添加一个逻辑元素,从多个源中进行选择,并将其中一个源引导到目标。这种选择通常是

使用数据选择器。附录A描述了多路复用器,它根据控制线的设置从多个输入中进行选择。控制线的设置主要基于从正在执行的指令中获取的信息。

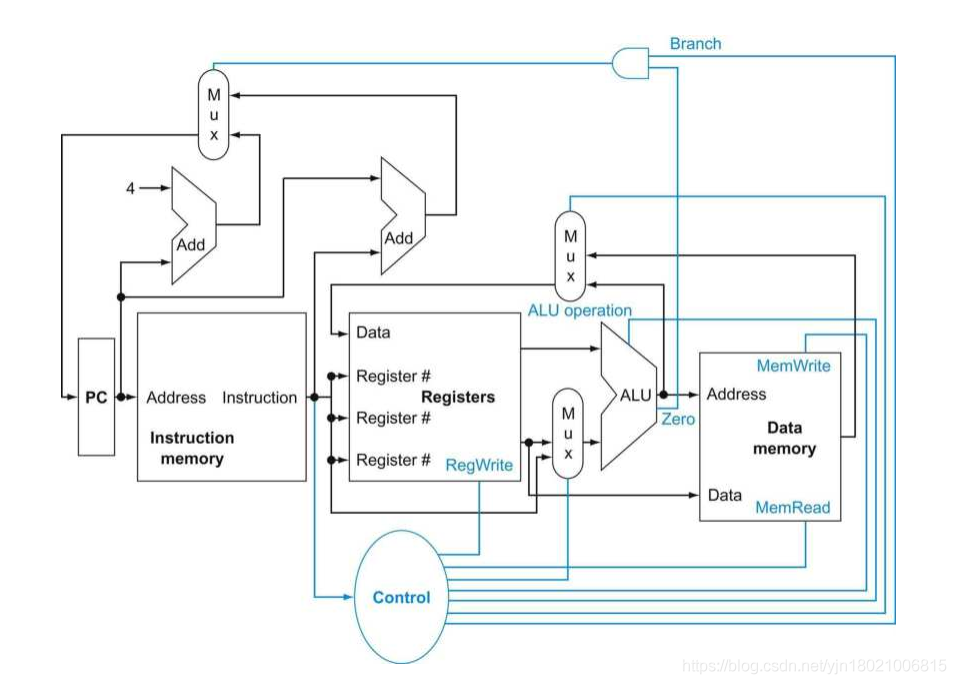

图4.1中的第二个遗漏是,必须根据指令类型控制几个单元。例如,数据存储器必须在加载时读取,在存储时写入。寄存器文件只能在加载或算术逻辑指令上写入。 图4.2

图4.2显示了图4.1的数据路径,其中增加了所需的多路复用器,以及主要功能单元的控制线。以指令为输入的控制单元

A control unit, which has the instruction as an input, is used to determine how to set the control lines for the functional units and two of the multiplexors(选择器)

决定PC+4或分支目的地址是否写入PC的top multiplexor是基于ALU的零输出设置的,ALU用于执行beq指令的比较。这个 RISC-V指令集的规则性和简单性意味着可以使用简单的解码过程来确定如何设置控制线

第4.3节和第4.4节描述了一种简单的实现方法,它对每条指令使用一个长时钟周期,并遵循图4.1和4.2的一般形式。

在第一种设计中,每条指令在一个时钟边缘开始执行,在下一个时钟边缘完成执行.这虽然更容易理解,但这种方法并不实用,因为必须严格延长时钟周期以适应最长的指令。

在为这台简单的计算机设计控件之后,我们将研究流水线实现及其所有复杂性,包括异常。

本篇完,感谢关注:RISC-V单片机中文网 |  /2

/2