有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

本帖最后由 皋陶 于 2020-8-27 14:04 编辑

根据RISC-V规范整理的几个文档。

1. 原文链接

https://riscv.org/specifications/

https://riscv.org/specifications/privileged-isa/

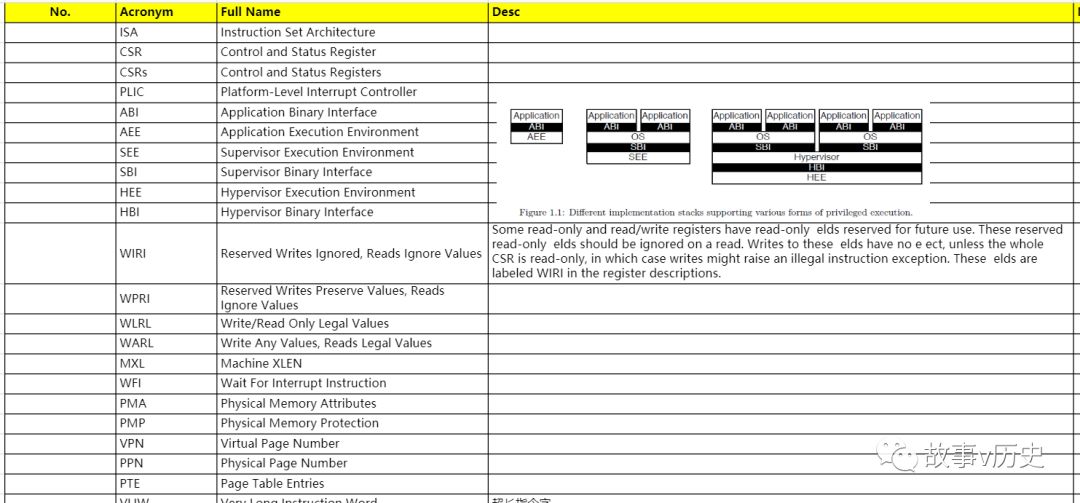

2. Definitions, acronyms and abbreviations

https://docs.qq.com/sheet/DUVBNaEVCUWxwV1Bi?tab=ox0pnu

3. User-Level ISA

https://docs.qq.com/sheet/DUURFZHNJZ0tFbVFJ?tab=tnsf3g

4. Assembly Programmer's Handbook

https://docs.qq.com/sheet/DUVpLQWdBSlpXdG12?tab=tnsf3g

5. CSRs

https://docs.qq.com/sheet/DUURQVEFJVmdOcVZI?tab=tnsf3g

6. Privileged Instructions

https://docs.qq.com/sheet/DUWFNcFFPVXFEVm9X?tab=hrpw36

7. Introduction

摘录自The RISC-V Instruction Set Manual Volume I: User-Level ISA, Chapter 1:

RISC-V (pronounced \risk-ve") is a new instruction set architecture (ISA) that was originally designed to support computer architecture research and education, but which we now hope will also become a standard free and open architecture for industry implementations. Our goals in dening RISC-V include:

- A completely open ISA that is freely available to academia and industry.

- A real ISA suitable for direct native hardware implementation, not just simulation or binary translation.

- An ISA that avoids \over-architecting" for a particular microarchitecture style (e.g., microcoded, in-order, decoupled, out-of-order) or implementation technology (e.g., full-custom, ASIC, FPGA), but which allows ecient implementation in any of these.

- An ISA separated into a small base integer ISA, usable by itself as a base for customized accelerators or for educational purposes, and optional standard extensions, to support general-purpose software development.

- Support for the revised 2008 IEEE-754 foating-point standard [14].

- An ISA supporting extensive user-level ISA extensions and specialized variants.

- Both 32-bit and 64-bit address space variants for applications, operating system kernels, and hardware implementations.

- An ISA with support for highly-parallel multicore or manycore implementations, including heterogeneous multiprocessors.

- Optional variable-length instructions to both expand available instruction encoding space and to support an optional dense instruction encoding for improved performance, static code size, and energy efficiency.

- A fully virtualizable ISA to ease hypervisor development.

- An ISA that simplies experiments with new supervisor-level and hypervisor-level ISA designs.

本篇完,感谢关注:RISC-V单片机中文网

|

/2

/2