有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

这篇文章大致可以分成两个部分:

第一部分叙述了RISC-V指令集架构的灵活性,指出此指令集依靠其基本指令集及多种扩展指令集的组合,可以实现几十种RISC-V处理器核,常规的验证流程已不可用,顺势提出Codasip公司的自动化设计流程,高度的自动化流程省时省力,同时设计灵活的配置层应对RISC-V的灵活性,致力于覆盖RISC-V处理器的所有组合。

第二部分主要阐述了Codasip和Mentor在提高仿真速度减少时间成本的方面所做的努力: 1. IA模型生成黄金预测模型,不考虑微架构实现细节,提高仿真性能; 2. simulation与emulation结合混合仿真,利用硬件并行机制提高验证效率; 3. 使用FlexMEM缩减上千程序依次从软件烧入硬件的时间;将黄金预测模型从软件平台取出,使其与硬件仿真平台并行运行,以减小事物在软件硬件之间的传输对仿真速度的影响(附图为验证环境)。

· 正 · 文 · 来 · 啦 ·

RISC-V 是一种新的ISA(指令集架构),它的发布使得处理器体系结构设计更加灵活,而且RISC-V应用领域覆盖嵌入式系统,物联网,高端手机和仓库云等众多领域,这样就可以使用一种指令集架构为这些领域量身定做处理器。伴随着这种灵活性的扩展而来的挑战,是验证时必须考虑到RISC-V处理核的所有可能性。在这篇文章中,Codasip 和Mentor旨在描述他们对于RISC-V处理器的验证方法,这种验证方法基于标准技术的组合,比如UVM和硬件仿真,和针对RISC-V验证提出的新概念,比如配置层,黄金预测层以及FlexMem方法。

介绍 RISC-V最初只是加州大学伯克利分校设计的一种免费开源指令集架构,研发的目的是教学与科研,但现在已经和ARM核一样商业化了,现在由RISC-V基金会维护。RISC-V指令集架构非常灵活,因为它除了基本的指令集(“I”/“E”),还支持众多扩展指令集,比如整数乘法与除法指令扩展集(”M”),原子操作指令扩展集(”A”),浮点指令扩展集(”F”),双精度浮点指令扩展集(D),四精度浮点指令扩展集(Q)等,通过它们的组合可以创造出数以百计可用的指令集。

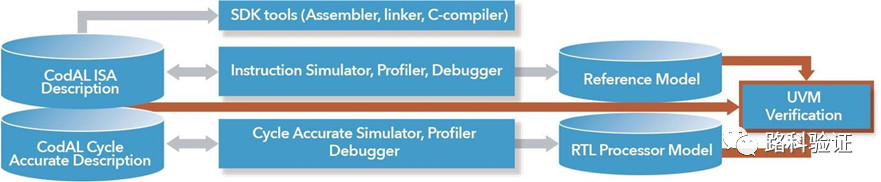

Codasip是家生产RISC-V IP核的公司,公司内部命名为Codix Berkelium(BK)。和现代处理器标准设计流程不一样,Codasip的设计流程高度自动化,流程可参考图1. Codasip使用一种架构描述语言CodAL,在更抽象的层次上描述处理器。

每一种处理器都用两种CodAL 模型描述,分别是Instruction-accurate(IA)模型和Cycle-accurate(CA)模型。

IA模型描述了指令的语法语义和它们的功能行为,不涉及任何微体系结构细节。

CA 模型描述了微体系结构比如流水线设计,译码器,时序等。通过这两个CodAL模型,Codasip工具可以自动生成SDK(软件工具开发包)工具(汇编工具,链接器,C编译器,模拟器,分析器,调试器)以及RTL和UVM验证环境。

在UVM 中,IA模型被用作黄金预测模型,CA模型生成的RTL被用作DUT。

这样高层次的自动化允许非常快速地探索设计空间,并在几分钟之内使用所有的软件工具生成一款独一无二的处理器。

图1. Codasip 生成SDK,RTL,参考模型和UVM验证环境的模型

本文旨在证明RISC-V ISA的灵活性既带来了好处,也带来了挑战,尤其在验证方面。我们将展示如何使用适当的战略来克服这些挑战,包括以下几个阶段(在各章节中详细描述):

1.定义配置层:遍历RISC-V处理器所有可能的变体以便设计和验证 2.定义黄金预测层:基于ISA仿真器,减少RTL仿真成本 3.利用硬件仿真和FlexMem方法有效地执行所有的测试

为RISC-V设计和验证定义配置层 RISC-V核的变体可能性非常多,手动去实现和维护所有相应的RTL表示和UVM环境。

这个时候必须要考虑自动化,其类型依赖于RISC-V核配置的变化。本文给出了三种类型。

出于演示的目的,我们会使用Codasip Berkelium处理器的两种不同配置: a)bk3-32IM-pd b)bk3-32IMC-pd

“I”,”M”和”C”如第一节所描述的那样,表示标准RISC-V指令的扩展集,”p”表示使能硬件并行乘法器,”d”表示使能JTAG调试接口。在BK处理器配置中是否存在乘除扩展集,实际上只有处理器支持的指令在数量上的区别。

从RTL和UVM的角度来看,这意味着现有的RTL模块更长,指令解码器更加复杂。

然而,当使能压缩指令扩展集,就要给RTL中加许多新的逻辑块,并且需要一个专用的指令译码器。

这就要求便宜额外的RTL文件来描述这些新的逻辑块。

从UVM的角度,需要为压缩指令译码器编译一个新的UVM agent,并妥当的连接到其余的UVM环境中。

1.第一种选项是将配置层放在自动化流程的开头。

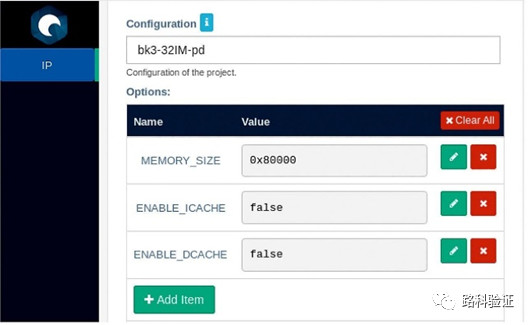

Codasip通过在高级别的CodAL语言描述中插入配置字符串来实现这一点。 图2展示了Codasip Studio(处理器开发环境)中的图形配置入口。

图中,配置字符串被破折号分为了三个部分,第一部分指定了处理器的名字和流水周期,第二部分包含了所用的ISA扩展集,最后一部分指定可用的硬件扩展。

(1)bk3-32IM-pd: 在CodasipStudio中输入bk3-32IM-pd的配置字符,所定义的处理器模型流水周期为3,并支持32bit位宽。支持的指令包括基本集成指令(”I”),乘除指令(”M”)。 硬件扩展有两个,包括并行乘法器(”p”)和JTAG调试接口(”d”)。

其他的设置如内存容量或者是否使能缓存,都能在这个窗口里找到。 配置完成后,就可以通过单击为这个指定的配置自动生成RTL 和UVM。

图2 用Codasip Studio中配置bk3-32IM-pd

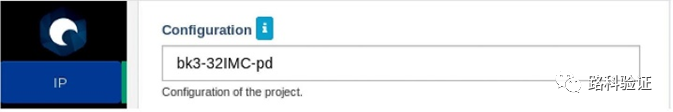

(2)bk3-32IMC-pd: 在Codasip Studio中配置bk3-32IMC-pd处理器时(如图3),使能压缩指令扩展集不会产生任何开销。唯一需要的操作是重构RTL 和UVM 环境,以便反映配置的变化。

图3 用Codasip Studio中配置bk3-32IMC-pd

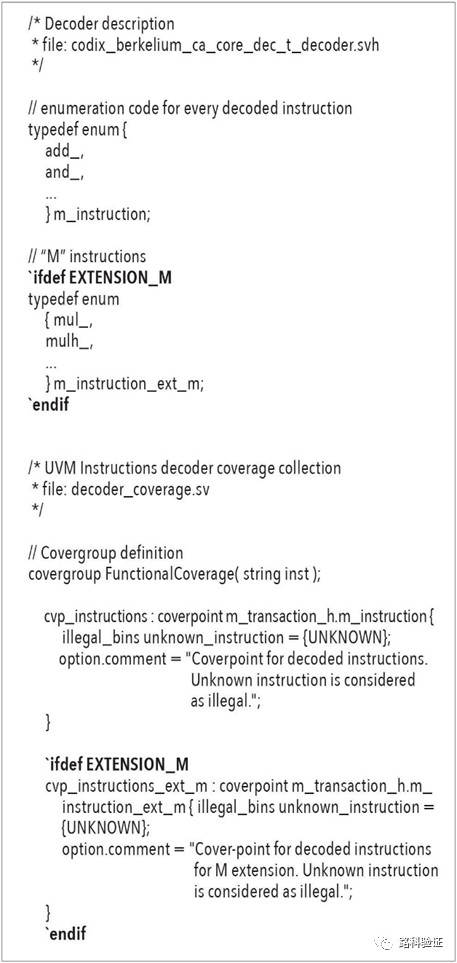

2.第二种选项适合手动写RTL和验证环境,是通过ifdef 结构和相关脚本来实现RTL和UVM的配置。 用这种方法,RISC-V的多种变体就只需要一种RTL 和验证环境。

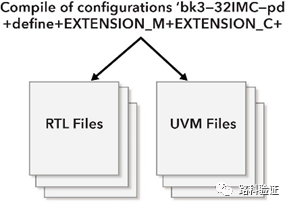

(1)bk3-32IMC-pd: 要编译源文件,我们使用RTL和UVM 常用的编译器定义选项,如图4所示。

如示例1中的代码所示,可以配置的各种扩展都包含在各自的定义块中,比如,’ifdefEXTENSION_M将”M”指令集放在decoder.svh 文件中。在编译时用+define+EXTENSION_M将文件编译进去,”M”指令集就能被译码器识别。

例中和覆盖率相关的部分也是一样的。因此,这种方法原则上允许开始验证之前的编译过程中配置UVM环境,更重要的是,它让为新的ISA或者硬件扩展配置UVM环境变得更容易些。

图4 使用Define命令编译所有文件

例1 bk-32IM-pd配置的ifdef部分的代码片段

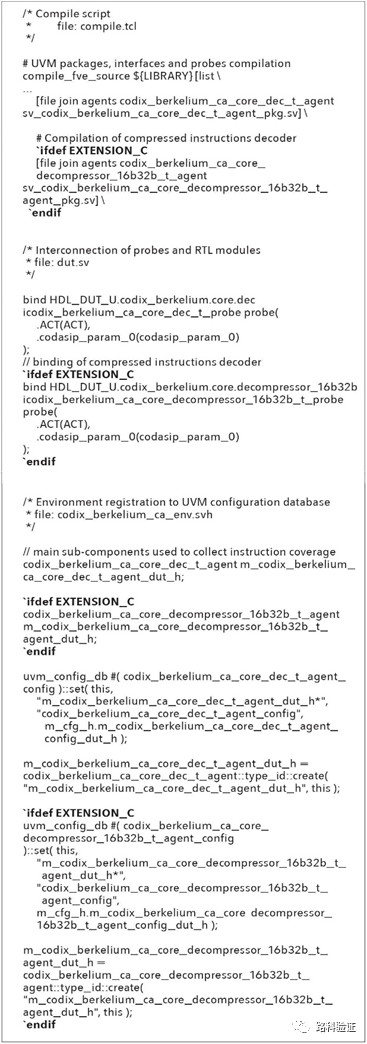

(2)bk3-32IMC-pd: 加入压缩指令扩展集的时候,有一点至关重要,那就是要确保压缩指令译码器的agent已经被编译和连接到环境中。

如例2,在compile.tcl文件中,’ifdef EXTENSION_C中的agent包包含了所有压缩指令译码器的agent文件,dut.sv文件中,’ifdef EXTENSION_C中连接agent和处理器RTL信号,在env.sv文件中,将agent注册到UVM环境中的配置数据库中。

例2 bk-32IMC-pd配置的ifdef部分的代码片段 |  /2

/2