|

3 开源蜂鸟E200 RISC-V介绍 蜂鸟E200系列处理器是中国大陆本土研发团队开发并第一个开源RISC-V处理器。蜂鸟是世界上最小的鸟类,其体积虽小却有着极高的速度与敏锐度,可以说是 “能效比”最高的鸟类。E200系列以蜂鸟命名便寓意于此,旨在将其打造成为一款世界上最高能效比的RISC处理器。 蜂鸟E200专为IoT领域量身定做,其具有2级流水线深度,功耗和性能指标均不逊于目前主流商用的ARM Cortex-M系列处理器,且免费开源,能够在IoT领域大有可为。有关蜂鸟E200处理器的具体信息请参见GitHub网址:https://github.com/SI-RISCV/e200_opensource,在后文中简称为“e200_opensource项目”。

4 蜂鸟E200的协处理器接口EAI 蜂鸟E200处理器核的协处理器机制借鉴了开源RISC-V处理器Rocket Core的协处理器接口RoCC(Rocket Custom Coprocessor),且接口信号定义非常类似.为了将其与原始的RoCC接口进行区分,命名为EAI(Extension Accelerator Interface)。本节将以一个实际案例来详细阐述如何使用EAI接口和Custom指令扩展出蜂鸟E200协处理器。

注意:由于蜂鸟E200处理器核基于Custom指令进行协处理器扩展,因此本文将Custom指令也称之为EAI指令。

4.1 EAI指令的编码

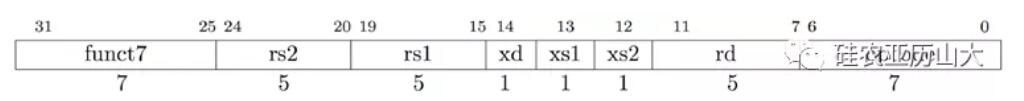

图1 EAI指令编码格式

32位的EAI指令编码格式如图1所示,要点如下:

如果xs1位的值为1,则表示该指令需要读取由rs1比特位索引的通用寄存器作为源操作数1;如果xs1位的值为0,则表示该指令不需要源操作数1。 同理,如果xs2位的值为1,则表示该指令需要读取由rs2比特位索引的通用寄存器作为源操作数2;如果xs2位的值为0,则表示该指令不需要源操作数2。 如果xd位的值为1,则表示该指令需要写回结果至由rd比特位指示的目标寄存器;如果xd位的值为0,则表示该指令无需写回结果。

4.2 EAI接口信号 限于篇幅和为了避免陷入过多技术细节,EAI接口的具体信号本文在此不做介绍,感兴趣的读者可以查阅e200_opensource项目doc目录下的Hummingbird_E200_Coprocessor_Extension_Quick_Start_Guide.pdf

4.3 EAI流水线接口 限于篇幅和为了避免陷入过多技术细节,EAI指令在流水线中的执行过程本文在此不做介绍,感兴趣的读者可以查阅e200_opensource项目doc目录下的Hummingbird_E200_Coprocessor_Extension_Quick_Start_Guide.pdf

4.4 EAI存储器接口 支持协处理器访问存储器资源可以扩大协处理器的类型范围,使得协处理器不仅限于运算指令类型。在蜂鸟E200处理器的LSU模块中为EAI协处理器预留了专用的访问接口。因此基于EAI接口的协处理器可以访问主处理器能够寻址的数据存储器资源,包括ITCM、DTCM、系统存储总线、系统设备总线以及快速IO接口等。 限于篇幅和为了避免陷入过多技术细节,EAI指令访问存储器资源的实现机制本文在此不做介绍,感兴趣的读者可以查阅e200_opensource项目doc目录下的Hummingbird_E200_Coprocessor_Extension_Quick_Start_Guide.pdf

4.5 EAI接口时序 限于篇幅和为了避免陷入过多技术细节,EAI接口的若干典型时序本文在此不做介绍,感兴趣的读者可以查阅e200_opensource项目doc目录下的Hummingbird_E200_Coprocessor_Extension_Quick_Start_Guide.pdf

5 蜂鸟E200的协处理器参考示例 本节将通过参考示例,阐述蜂鸟E200处理器如何使用EAI接口定义并实现一个协处理器。注意:本参考示例来源于Rocket-Chip开源项目的一个协处理器教学示例。

|  /2

/2