有人预言,RISC-V或将是继Intel和Arm之后的第三大主流处理器体系。欢迎访问全球首家只专注于RISC-V单片机行业应用的中文网站

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

本帖最后由 新ちゃん 于 2020-10-9 09:15 编辑

作者:印度本科生Shivam Potdar

大家好,我是来自印度卡纳塔克邦国立技术学院的高级EE本科生Shivam Potdar。大约一年前,我通过CS61C和UC Berkeley的课程内容介绍了RISC-V 。然后,我有机会作为自由和开源硅基金会(FOSSi)的Google Summer of Code(GSoC)学生,探索几种新颖的技术,这些技术与RISC-V一起将塑造我们的未来行业。现在,它已成为知识和探索的永无止境的旅程。

我是Shivam Potdar,来自印度卡纳塔克国立理工学院的EE大四学生。大约一年前,通过加州大学伯克利分校CS61C的课程内容,我接触到了RISC-V。

然后,我得到了一个机会,作为自由和开源硅基金会(FOSSi)的Google Summer of Code (GSoC)学生,探索了几项新技术,这些技术加上RISC-V,将塑造我们行业的未来。现在,它已经变成了一个永无止境的知识和探索之旅。

GSoC是谷歌资助的一个项目,鼓励学生为开源项目做贡献。由于RISC-V的成立以及FOSSi、lowRISC、Symbiflow、BeagleBoard.org等组织,开源硬件项目的参与度越来越高。

RISC-V最令人兴奋的一个方面是它为多个领域的新想法提供了一个开放的场所。它已经成为OpenTitan等架构创新的首选,也成为展示诸如Chisel(Rocket芯片、SiFive内核)、SpinalHDL(VexRiscv)、BlueSpec(Shakti处理器)等新HDL的首选。

以下是我在这个暑假期间所作的一些探索:

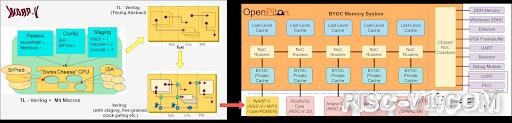

我致力于增强一个名为WARP-V的RISC-V内核,采用TL-Verilog的前瞻性设计方法,并与OpenPiton(一个用SystemVerilog编写的开源多核框架)集成。

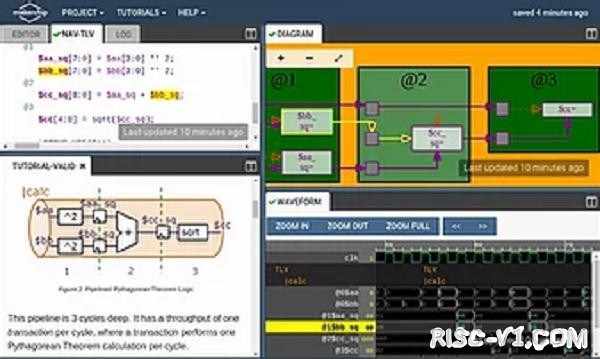

TL-Verilog是对SystemVerilog的革命性扩展,由我的GSoC导师Steve Hoover领导。它在事务层面对系统进行建模,具有时序抽象、高度可参数化、灵活、易学习/调试/文档的特点,并显著减少了代码大小。它既不是HLS,也不是应用于硬件的编程语言,而是一个具有现代特征的抽象,使建模非常接近硬件。

Makerchip.com是一个免费的基于Web的TL-Verilog集成开发环境,它支持设计、调试、仿真和Verilog转译都在浏览器标签中完成!WARP-V主要是在这个平台上开发的。SandPiper是TL-Verilog的编译器,将其翻译成可综合的(System)Verilog,与开放源代码和经过行业验证的设计流程兼容。

在学校里,我花了几个星期的时间进行设计和调试,才用 Verilog / VHDL 完成了一个基本的MIPS实现。另一方面,我是由Steve和Kunal Ghosh组织的“RISC-V 30小时内为你服务(MYTH)”研讨会的中的助教。大约有200名参与者,其中许多人没有数字设计的背景,他们学习了RISC-V,并在短短五天内为社区贡献了35个TL-Verilog核。我将在10月8日的VSDOpen 2020上再次帮助举办类似的研讨会,该研讨会将在1.5小时内来介绍TL-Verilog!

WARP-V在TL-Verilog中提供了一个高度可配置的CPU,支持各种流水线深度,WARP-V在TL-Verilog中呈现了一个高度可配置的CPU,支持各种流水线深度、长延迟指令、分支预测、时钟门控、内联汇编器,甚至是多个ISA! 对于RISC-V,内核支持RV32I[M][F],也通过了riscv-formal的正式验证。

它还使用Steve的定制逻辑即服务项目--1st CLaaS在AWS FPGA上进行了表征和测试。对于RISC-V,内核支持RV32I [M] [F],该产品也已通过riscv-formal进行了正式验证。还使用Steve的定制逻辑即服务项目1st CLaaS在AWS FPGA上对它进行了仿真和测试。

OpenPiton是一个多核研究平台,通过向内核提供内存子系统、IO接口、缓存和共享资源来支持异构ISA。它兼容SPARC、RISC-V和x86,以及已有的几种外设。

暑假期间,我致力于在WARP-V中添加RISC-V M型扩展,对其进行正式验证,并通过支持长等待时间指令并提供外部存储器接口来为OpenPiton集成做准备。

在过去的几个月里,我可以观察到RISC-V的巨大增长速度。这个生态系统是如此的开放和包容,以至于我今天成为了RISC-V国际的社区成员,并参与各种在线聚会、网络研讨会和全球论坛等活动。

今天,我们可以通过Symbiflow、Openlane、Yosys、Verilator和Skywater PDK等FOSS工具来执行整个RTL到GDS的流程,包括FPGA仿真、模拟和制造。这些工具和技术(如TL-Verilog与RISC-V搭配)所支持的现代方法论确实将改变半导体产业。

有人恰当地将RISC-V表示为硬件的Linux。令人振奋的是,看到硬件的民主化和行业变化的动态,如今,即使是无晶圆厂的初创企业也可以与老牌巨头竞争。作为一名即将进入该领域的学生,RISC-V的前景一片光明。

看了以上内容,总感觉和前一段时间刷屏的国科大本科生RISC-V流片的不太一样,感觉到我们更加偏重于应用实现,而这个印度学生所作的更像是在做更多的研究与探索。虽然没有流片,但是总体来说这个印度本科生所做的并不比我们差。

完

|  /2

/2